# Multiplexing cross-connector E1-DXC

## **Features**

- Desktop or the card for 19" 3U Cronyx rack

- Four E1 links (PCM-30)

- Distance up to 1,5 km (up to 2,5 km for rack design)

- 128 x 128 non-blocking switching matrix

- G.704 frame structure

- CAS and CRC4 multi-frame structure

- Sa bits cross-interchange

- Clock source from the built-in oscillator, from any E1 receiver, or from the digital interface

- Master and backup clock

- Synchronous V.35, RS-530, RS-449, RS-232, X.21, Ethernet interface, or and IDSL modem in place of one of the E1 links

- Asynchronous mode for the RS-232 interface

- Built-in HDLC buffer for models with a synchronous V.35, RS-530, RS-449, RS-232, or X.21 interface

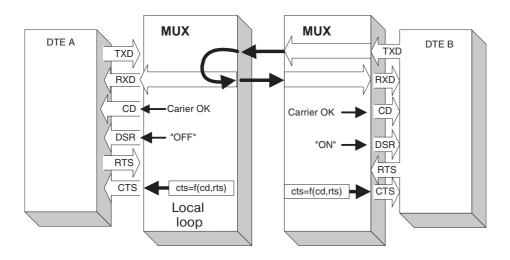

- Local loop

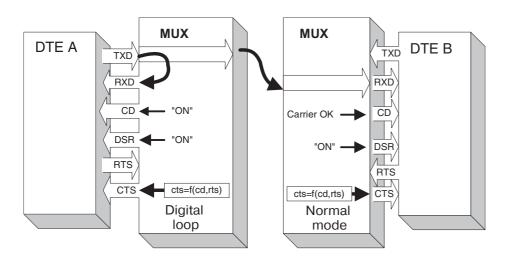

- Digital loop for models with a V.35, RS-530, RS-449, RS-232, or X.21 interface

- Built-in Bit Error Rate Tester (BER tester);

- RS-232 port for monitoring and control

- "Dry contact" alarm signaling (for desktop models only)

- Built-in power supply unit from mains or battery

- Upgradable firmware

- SSE Certificate of the State Communications Committee of the Russian Federation No. OS/1-SPD-19

# **Contents**

| Technical specifications       | 3  |

|--------------------------------|----|

| Description                    | 4  |

| Delivered items                |    |

| Firmware upgrade               | 5  |

| Order code                     | 5  |

| Controls and indicators        | 6  |

| Front panel indicators         | 6  |

| Jumpers                        |    |

| Line impedance                 |    |

| Programming mode               |    |

| Console                        |    |

| Configuration parameters       | 8  |

| Saving settings                |    |

| Device synchronization         |    |

| Timeslot 16 mode               |    |

| Timeslot interchange map       | 8  |

| Sa bits interchange map        | 8  |

| Receiver path sensitivity      |    |

| CRC4 Multi-frame synchronism   |    |

| Idle Code                      | 8  |

| Loss of synchronization action | 8  |

| Digital port asynchronous mode | 8  |

| HDLC buffer                    | 8  |

| Clock inversion                | 9  |

| Receiver path synchronization  | 9  |

| CTS generation logic           | 9  |

| Ethernet packet filtering      |    |

| Ethernet interface mode        | 9  |

| DTE emulation                  | 9  |

| DTE1 emulation mode            | 9  |

| DTE2 emulation mode            | 10 |

| Clock parameter requirements   | 11 |

| X.21 interface                 | 11 |

| Ethernet interface             | 12 |

| Loops                          | 13 |

| Normal operations              |    |

| Local loop                     |    |

| Digital loop                   |    |

| Emergency alarm                |    |

| Rear panel connectors          |    |

| Control via the console        |    |

| Synchronous data transfer.     |    |

| Cable diagrams                 |    |

| Caule diagrams                 | ∠0 |

# **Technical specifications**

| Digital interface                       |                                                        |

|-----------------------------------------|--------------------------------------------------------|

| Data transmission rate                  | 64 to 1984 kbit/sec (Nx64)                             |

| Clock signals                           |                                                        |

| Modem signals                           |                                                        |

| Ethernet interface (for the E1-DXC/B/3E |                                                        |

| Interface type, connector               |                                                        |

| Bandwidth                               |                                                        |

| Operating modes                         |                                                        |

| Filtering rate                          | 15000 frames per second                                |

| Maximum frame size                      | 1518 bytes, including the MAC layer header and the CRC |

| LAN table size                          | 10000 MAC-addresses                                    |

| Ethernet interface (for the E1-DXC/B/3E |                                                        |

| Interface type, connector               |                                                        |

| Bandwidth                               |                                                        |

| Operating modes                         | 100 Mbps Full Duplex, 100 Mbps Half Duplex,            |

| -1 - 6                                  | 10 Mbps Full Duplex, 10 Mbps Half Duplex, or           |

|                                         | Autonegotiation                                        |

| LAN table size                          | 15000 MAC-addresses                                    |

|                                         | 4228 bytes, including the MAC layer header and the CRC |

|                                         | Transparent or Cisco-HDLC bridging IEEE protocol,      |

|                                         | automatically selected                                 |

| E1 interface                            | ·                                                      |

| Encoding                                | HDB3                                                   |

| Line impedance                          |                                                        |

|                                         | 120 Ohms, symmetrical (twisted pairs)                  |

|                                         | 120 Ohms symmetrical (twisted pairs), or               |

|                                         | 75 Ohms unsymmetrical (coaxial), jumper-selectable     |

| Signal level at the receiver input      | , , , , ,                                              |

|                                         | 0 to -36 dB (up to 1,5 km over 0,6 mm twisted pairs)   |

|                                         | 0 to -43 dB (up to 2,5 km over 0,6 mm twisted pairs)   |

| Transmitter path synchronization        | from the built-in oscillator, or                       |

|                                         | from the E1 link receiver, or from the digital port    |

| Jitter attenuator                       | in the receiver or transmitter path, attenuation up to |

|                                         | 120UIpp                                                |

|                                         | according to G.704 (CRC4, CAS multi-frames)            |

| Link rate negotiation                   |                                                        |

| Connector                               |                                                        |

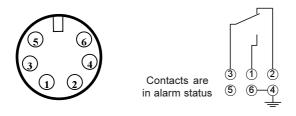

| Emergency alarm interface (for desktop  | design models)                                         |

| Relay contact current                   | up to 250 mA                                           |

| Relay contact voltage                   |                                                        |

| Connector                               | Mini DIN, 6 pins (female)                              |

| Control port                            |                                                        |

| Interface type, connector               | RS-232, DB9 (female)                                   |

| Data transmission protocol              | asynchronous, 9600 bit/sec, 8N1                        |

| Diagnostic modes                        |                                                        |

| Loops                                   | local (on the G.703 line) or                           |

|                                         | digital (on the digital interface)                     |

|                                         | enabled via the control port                           |

| BER-tester                              | 1                                                      |

# **Description**

The Cronyx E1-DXC multiplexing cross-connector is designed for timeslot interchange between any of the four E1/PCM30 links. Interchange is performed according to a user-specified map.

According to the selection made by the user, one of the E1 ports of the multiplexing cross-connector may be replaced by a RS-530, RS-232, V.35, or X.21 interface with standard connectors, by a universal interface, or by a built-in Ethernet module or IDSL modem. The universal interface supports RS-232, RS-530, RS-449, RS-422, V.35, and X.21 standards, and is equipped with a HDB44 connector (MDS36 connector in 19" rack design models), the interface type in this case is determined by the connected cable. Cronyx E1-DXC with Ethernet interface contains the Remote Bridge module, and may be used together with another Cronyx E1 series device equipped with Ethernet interface for interconnection of two LANs.

In order to provide proper data transmission, the multiplexing cross-connector provides equal delay for timeslots constituting the common data transmission link.

The multiplexing cross-connector configuration settings are performed via the control port equipped with RS-232 interface (control and monitoring for rack design models is possible via RMC board). Configuration parameters are stored in EEPROM of the device.

Capability to enable loops over E1 links is provided for testing E1 links.

The multiplexing cross-connector has the capability to upgrade its firmware via the console port. New firmware revisions allow to expand multiplexer's capabilities. Loading special firmware revisions allows to change multiplexer's functional capabilities completely. Upgrades are available from the Cronyx Web-server - www.cronyx.ru.

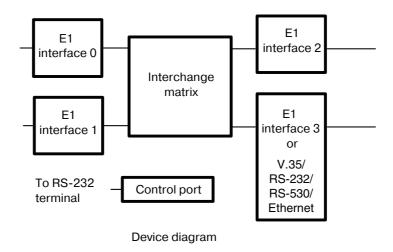

Device structural diagram is presented below.

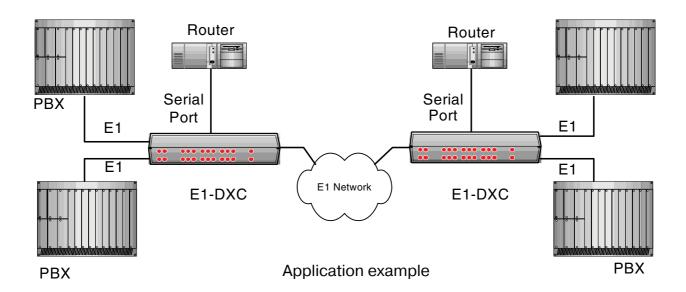

Below is an example of using E1-DXC. The figure shows the simultaneous connection of routers and office exchanges over a single link.

### **Delivered** items

Delivered items include:

- The E1-DXC multiplexing cross-connector

- Removable terminals for connecting to E1 lines

—4 pcs. (3 pcs. for models equipped with a digital port)

- Power cable (for desktop design models with AC mains power supply)

- User's guide

# Firmware upgrade

The multiplexer's firmware may be upgraded using a PC and special software, via console port. The firmware is available from Web-server located at www.cronyx.ru. The detailed loading procedure instructions are supplied with the firmware.

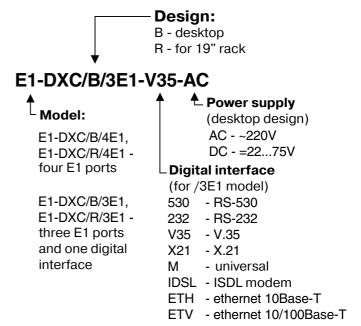

#### Order code

# **Controls and indicators**

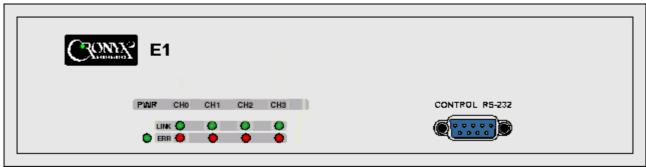

### Front panel indicators

The PWR indicator shows the mains power supply.

The DI indicator (for rack design models only) shows the presence of the interface board.

Two indicators are used to show the status of each of the four ports: LINK (green) and ERR (red).

The LINK lights when the line carrier is present (for an E1 port), if the cable is connected (for the Ethernet port), or shows the RTS signal status (for the digital port). When loop or BER tester is enabled, the corresponding LINK indicator flashes.

The ERR indicator of the E1 port lights during line signal loss, during frame of multi-frame synchronization loss, or when there are errors in the line, if the BER tester is enabled. The ERR indicator flashes if there is a loss of frame (bit A of timeslot zero) or CAS multi-frame (bit of timeslot 16) synchronization on the remote device.

The ERR indicator of the Ethernet port lights during the overflow of bridge internal buffers.

The ERR indicator of the serial port lights during FIFO buffers overflow or underflow.

During loss of the master clock, the device switches to the backup clock source, and the LINK and ERR indicators of the corresponding port flash. If both clocks (master and backup) are lost, the device switches to the internal oscillator, then the LINK and ERR indicators of the source ports will flash.

### **Jumpers**

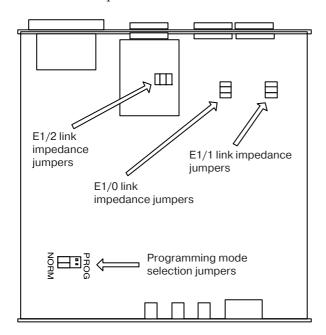

Jumper location on multiplexer's printed circuit board is shown on figures below.

In order to move jumpers in desktop design devices, the device upper cover should be taken off after removing mounting screws.

Attention!!! Before removing the cover, make sure the device is disconnected from the power source.

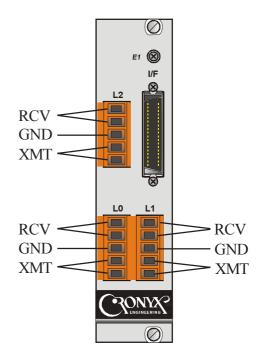

Front panel of the 19" rack design device

Front panel of the desktop design multiplexing cross-connector

#### Line impedance

The desktop design multiplexer is delivered in configuration for twisted pair (120 Ohms). E1 line impedance is selected by jumpers, there are three jumpers per link. The jumpers must be removed for twisted pair, and installed for coaxial cable (75 Ohms).

The 19" rack design multiplexing cross-connector is not equipped with line impedance selection jumpers, and is designed to operate over twisted pairs (120 Ohms)

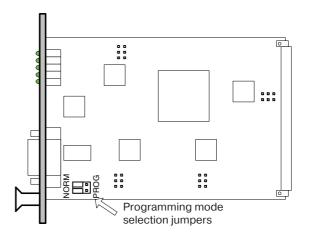

#### Programming mode

Before loading a new firmware revision, two internal jumpers must be switched from the "NORM" position to the "PROG" position. After completing the programming procedure, the jumpers must be returned to the "NORM" position.

Jumper locations for desktop design models

#### Console

The front panel of the multiplexer is equipped with a DB9 connector for connecting a control terminal (console) with a RS-232, 9600 bit/sec, 8 bits, no parity interface. The console may be used for viewing current device modes, link states, error statistics, for selecting device modes, and for storing them in the nonvolatile RAM.

Jumper locations for 19" rack design models

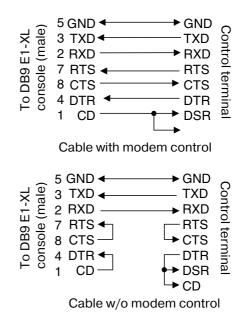

The console connector has a standard pinout. When connecting the terminal, the presence of CD and CTS signals must be provided. It is recommended to use the following cable diagrams:

# **Configuration parameters**

Each time the multiplexing cross-connector is switched on, it is configured according to specified parameters. The configuration parameters specified from the console, are stored in the NVRAM.

#### Saving settings

Device parameters are stored in the nonvolatile RAM (NVRAM). When the device is switched in, the last saved parameters are set.

#### Device synchronization

The synchronization source may be one of the following:

- internal oscillator (Int)

- any of the E1 links (Link...)

- digital port (Port, for equipped models).

The master clock and the backup clock are specified for the device. When the master clock is lost, the device switches to the backup one. If both master and backup clocks are lost, the device switches to the internal oscillator.

Attention! The digital port should not serve as the backup clock.

#### Timeslot 16 mode

The sixteenth timeslot may be used for data transmission (Data) or for telephone signaling transmission (CAS).

#### Timeslot interchange map

When editing the Timeslot Interchange Map there is a capability to direct data from any incoming timeslot to any outgoing one. The delay mode is specified during this:

- Voice (minimum delay mode). This mode is used for timeslots containing independent 64 kbit/sec data streams (such as voice data).

- Data (fixed delay mode). This mode must be selected for all timeslots, which are used to transmit a common N x 64 kbit/sec data stream (N > 1). Otherwise, the integrity of this data stream may be violated.

Attention! The fixed delay mode is always selected in rack design models.

### Sa bits interchange map

The Sa bit interchange map  $(S_{a4}-S_{a8})$  may be specified in the multiplexing cross-connector. The Sa bit source may be any Sa bit of any E1 link, or the value of "1" is transmitted in the corresponding position.

#### Receiver path sensitivity

E1 link receiver path sensitivity may be set to one of the following two values: -12 or -36 dB (-43 dB for rack design models).

### CRC4 multi-frame synchronism

When specifying configuration parameters for each E1 port, it is possible to enable or disable CRC4 multi-frame synchronization control.

#### Idle Code

When specifying the interchange map, the idle code is specified in non-interchanged timeslots. The idle code is entered and displayed in hexadecimal format, and is specified for each E1 port.

#### Loss of synchronization action

When specifying configuration parameters, it is possible to select on of the two responses to loss of E1 link synchronization:

- Remote Alarm bit A of timeslot zero is set in the transmitted E1 frame.

- AIS the AIS alarm indication signal ("blue code") is transmitted.

#### Digital port asynchronous mode

The digital port may support both the asynchronous and the synchronous data transmission modes. When specifying port configuration parameters in the asynchronous mode, one of the following rates may be selected: 1200, 2400, 4800, 9600, 19200, 38400, 57600, or 115200 bit/sec. The 8N1, 7P1, 8P1 asynchronous symbol formats are supported.

#### HDLC buffer

For information that is more detailed see section "Synchronous data transmission".

This parameter is not used for Ethernet interface multiplexer.

#### **Clock inversion**

In models equipped with the digital port, when using INT or From Link clock, the TXD data are delayed in relation to the TXC clock. The total time shift is comprised of the delay in the cable, and the delay in the digital interface of the equipment connected to the E1-DXC. As a result, data errors may appear when selecting some rates.

This problem may be solved in the following way:

- TXC inversion by changing settings of the equipment connected to the E1-DXC;

- change of cable length;

- reversal of TXC-a and TXC-b pins on one of the interface cable connectors;

- selecting TxC clock inversion.

The same problem may appear when using external clock from the ERC receiver path. It may be solved in the same way:

- change of cable length;

- reversal of ERC-a and ERC-b pins on one of the interface cable connectors;

- selecting ERC clock inversion. For information that is more detailed see section "Synchronous data transmission".

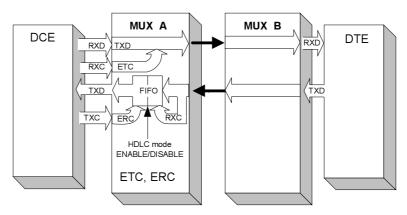

#### Receiver path synchronization

Receiver path synchronization for the digital port may be set to one of the following modes:

- from E1 link receiver

- from external clock (ERC)

The receiver path synchronization from the external source mode is used when connecting to DCE devices, which do not have external synchronization from the digital port (RS-232, V.35, RS-530) mode. In this case the modem outputs clock data received at the ERC input. The FIFO buffer is used to correct data phase at the RXD digital port output in relation to ERC clock. For the correct operation of the buffer (no overflows or underflows), the clock frequency received from the line must be the same as the frequency at the ERC input. This condition is maintained when the data transmission link has a common clock source. Otherwise there may be periodic errors related to FIFO buffer overflows or underflows. The frequency of these errors

depends on the discrepancy value between these two frequencies. In cases when it is not possible to provide common clock, and the data transmitted over the network comply with the HDLC protocol, the HDLC mode of the FIFO buffer must be used.

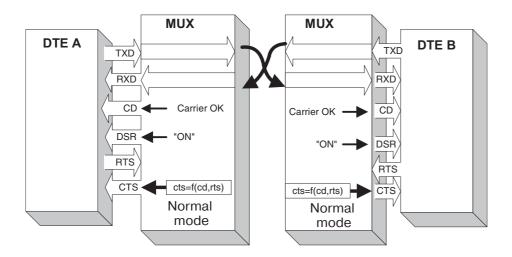

#### CTS generation logic

When specifying configuration, it is possible to select one of the four rules for CTS output signal generation: CTS=1, CTS=CD, CTS=RTS, or CTS=CD\*RTS.

#### Ethernet packet filtering

In some cases Ethernet packet filtering must be disabled for network administration, monitoring or testing purposes.

When filtering is enabled, the Ethernet bridge is used only to transmit frames filtered by destination addresses. When filtering is disables, all frames are translated from one side of the bridge to the other.

#### Ethernet interface mode

The Ethernet interface in the E1-DXC/B/3E1-ETH model operates at a fixed rate (10 Mbps), and there is the capability to select Half Duplex or Full Duplex mode.

In the E1-DXC/B/3E1-ETV model there is the capability to select data transmission rate (10 Mbps or 100 Mbps), Half Duplex or Full Duplex mode, or select autonegotiation mode.

# **DTE** emulation

Two clock inputs - reception and transmission (ETC and ERC) are provided for connecting the E1-DXC multiplexer over RS-232, V.35, RS-530 interfaces to DCE devices in the synchronous mode. Only ETC is provided for the X.21 interface.

#### DTE1 emulation mode

The DTE1 emulation mode is used when connecting to DCE devices, which have external synchronization from the digital port (RS-232, V.35, RS-530, X.21) mode. In this case, a pair of devices connected over the digital port (RS-232, V.35, RS-530, X.21) transparently translates the clock frequency.

#### DTE2 emulation mode

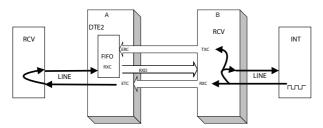

The DTE2 emulation mode is used when connecting to DCE devices, which do not have external synchronization from the digital port (RS-232, V.35, RS-530) mode. In this case the E1-DXC multiplexing cross-connector receives data to the digital port according to the clock received on the ETC input, and transmits according to the clock received on the ERC input. The FIFO buffer is used

to correct data phase at the RXD digital port output in relation to ERC clock.

For the correct operation of the buffer (no overflows or underflows) the clock frequency received from the line must be the same as the frequency at the ERC input. This condition is maintained when the data transmission link has a common clock source. Otherwise there may be periodic errors related to FIFO buffer overflows or

## Configuration parameters

| General parameters                         | D. III. 1 . 1 . 1 . 1 . 1             | . 10 1    | 12(0.0)                                       |

|--------------------------------------------|---------------------------------------|-----------|-----------------------------------------------|

| Master clock                               |                                       |           | ` /                                           |

| Backup clock                               |                                       | ınk2, Lı  | nk3                                           |

| Timeslot 16                                | *                                     |           |                                               |

| Timeslot interchange map                   |                                       |           | •                                             |

| Sa bits interchange map                    | non-blockable 20 x 2                  | 20 interc | change matrix                                 |

| E1 link parameters                         |                                       |           |                                               |

| CRC4 multi-frame synchronism               | Yes (enabled), No (                   | disable   | d)                                            |

| Response to loss of synchronization        | . The A bit of timeslot (AIS)         | t0(Rem    | ote Alarm), "blue code"                       |

| Receiver path sensitivity                  | 36 dB (-43 dB for                     | 19" racl  | k models), -12 dB                             |

| Idle code                                  | 0x00 - 0xFF                           |           |                                               |

| Digital port parameters                    |                                       |           |                                               |

| Operating mode                             | . Sync (synchronous)                  | , Async ( | (asynchronous)                                |

| Transmission rate in the asynchronous mode | . 1200, 2400, 4800,<br>115200 bit/sec | 9600, 19  | 9200, 38400, 57600,                           |

| Asynchronous symbol formal                 | . 8N1, 7P1, 8P1                       |           |                                               |

| Receiver path synchronization mode         | .RXC, ERC, HDLC                       | Buffer    |                                               |

| CTS signal generation mode                 | .CTS=1, CTS=CD,                       | CTS=R     | TS, CTS=CD*RTS                                |

| RXC/ERC clocks                             | . Normal,                             | Inverte   | d                                             |

| TXC/ETC clocks                             | . Normal,                             | Inverte   | d                                             |

| Ethernet port parameters                   |                                       |           |                                               |

|                                            | E1-DXC/B/3E1-ET                       | Ή         | E1-DXC/B/3E1-ETV                              |

| Operating mode                             | . 10 Mbps Half duple                  | ex,       | 10 Mbps Half duplex,                          |

|                                            | 10 Mbps Full duple:                   | X         | 10 Mbps Full duplex,<br>100 Mbps Half duplex, |

|                                            |                                       |           | 100 Mbps Full duplex,                         |

|                                            |                                       |           | Autonegotiation                               |

| Packet filtering                           | *                                     |           | Enabled,                                      |

|                                            | Disabled                              |           | Disabled                                      |

underflows. The frequency of these errors depends on the discrepancy value between these two frequencies. In cases when it is not possible to provide common clock, and the data transmitted over the network comply with the HDLC protocol, the HDLC mode of the FIFO buffer must be used.

### Clock parameter requirements

Clock may be received from the internal generator of the E1-DXC multiplexing cross-connector, or from digital port external clock input. The clock that is used to generate the E1 link output signal, determines such parameters as phase jitter and frequency accuracy. In those modes, when the E1-DXC multiplexing cross-connector is selected as the clock source, the multiplexer technical solutions guarantee, that phase jitter and frequency accuracy comply with the requirements of the corresponding ITU-T recommendations. If another device connected to the E1-DXC digital port (DTE emulation mode) is selected as the clock source,

then it is required to make sure that the clock parameters comply with ITU-T requirements.

# X.21 interface

The X.21 interface has electric signal characteristics complying with the ITU-T V.11 recommendation. The set of signals is different from other interfaces:

| X.21  | Signal         |

|-------|----------------|

| DB-15 |                |

| 2     | Transmit (A)   |

| 9     | Transmit (B)   |

| 4     | Receive (A)    |

| 11    | Receive (B)    |

| 7     | ETC (A)        |

| 14    | ETC (B)        |

| 6     | Sig Timing (A) |

| 13    | Sig Timing (B) |

| 3     | Control (A)    |

| 10    | Control (B)    |

| 5     | Indication (A) |

| 12    | Indication (B) |

| 1     | Shield         |

| 8     | GND            |

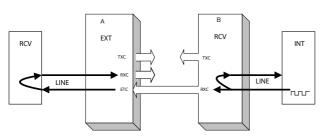

DTE1 emulation mode using external transmission clock

DTE2 emulation mode using external transmission and reception clock

Only one clock signal is used in the X.21 interface for received and transmitted data. In order to provide correct data reception, it is required to comply strictly with the requirements for common clock in the link.

The Indication signal corresponds to the CD signal, and the Control signal corresponds to the RTS signal.

# **Ethernet interface**

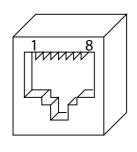

The E1-DXC/B/3E1-ETH model may be equipped with an Ethernet module with a 10Base-T port, and the E1-DXC/B/3E1-ETV model may be equipped with an Ethernet module with a 10/100BaseT port.

Two devices with Ethernet interface form a remote bridge, and are used for merging two LANs. The remote bridge has the packet filtering capability, that is, it is used to transmit only the packets, the addressees of which are absent from the LAN. Cronyx E1-DXC with an Ethernet interface may perform Ethernet packet compression by clearing packet augmenting bits, the length of which is less than the permitted one.

The remote bridge formed by two devices has the following characteristics:

|                     | ETH Module                                  | ETV Module                                                                                                        |

|---------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Connector type      | e RJ45 (female)                             | RJ45 (female)                                                                                                     |

| Modes               | 10 Mbps Half Duplex,<br>10 Mbps Full Duplex | 10 Mbps Half Duplex,<br>10 Mbps Full Duplex,<br>100 Mbps Half Duplex,<br>100 Mbps Full Duplex,<br>Autonegotiation |

| LAN table           | 10000 MAC-addresses                         | 15000 MAC-addresses                                                                                               |

| Max. size of frame  | 1518 bytes                                  | 4228 bytes                                                                                                        |

| Support<br>for VLAN | No                                          | Yes                                                                                                               |

| Protocols           | Transparent                                 | Transparent,<br>Cisco-HDLC bridging<br>IEEE protocol                                                              |

# Loops

# Normal operation

# Local loop

# Digital loop

# **Emergency alarms**

The emergency alarm interface is used for turning on en external executive unit (ringer, buzzer, console indicator, etc.) during emergency – for example, loss of bearer, loss of synchronization, power failure. It is switched on by "dry" (that is, not connects to any multiplexer electrical circuits) relay contacts.

When power supply and the carrier are present, contact 3 is connected to contact 1. During power or carrier loss, contact 3 breaks circuit 1 and connects to contact 2 (the "alarm" state).

Attention! The 19" design multiplexing crossconnector is not equipped with an emergency alarm interface.

Emergency alarm connector and diagram:

| Contact |                                     |

|---------|-------------------------------------|

| 1       | Connected to the middle contact (3) |

|         | during normal operation.            |

|         | Disconnected during error           |

| 2       | Disconnected during normal          |

|         | operations.Connected to the middle  |

|         | contact (3) during error.           |

| 3       | Middle contact                      |

| 4       | GND                                 |

| 5       | Reserved. Must not be connected.    |

| 6       | GND                                 |

# Rear panel connectors

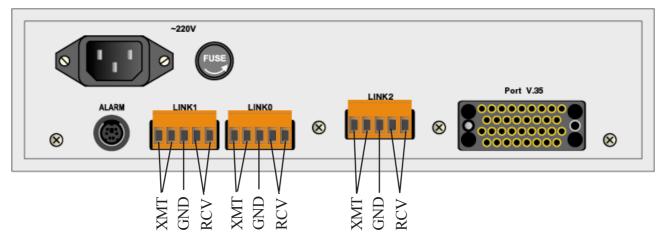

The rear panel contains the digital interface connector (for equipped models), and removable E1 link terminals.

Rear panel of the 19" rack device (E1-DXC/R/3E1-M)

In desktop design models digital port with a X.21 interface is equipped with a DB15 connector (female):

| DB-15 female | Signal | Direction |

|--------------|--------|-----------|

| 2            | T(A)   | Receive   |

| 9            | T(B)   | Receive   |

| 4            | R(A)   | Transmit  |

| 11           | R(B)   | Transmit  |

| 7            | ETC(A) | Receive   |

| 14           | ETC(B) | Receive   |

| 6            | S(A)   | Transmit  |

| 13           | S(B)   | Transmit  |

| 3            | C(A)   | Receive   |

| 10           | C(B)   | Receive   |

| 5            | I(A)   | Transmit  |

| 12           | I(B)   | Transmit  |

| 1, 8         | GND    | _         |

In desktop design models the digital port with RS-232 or RS-530 interface is equipped with a DB25 connector (female):

| Cont. DB25 | RS-530 | RS-232 | Direction. |

|------------|--------|--------|------------|

| 2          | TXD-a  | TXD    | Receive    |

| 14         | TXD-b  | _      | Receive    |

| 3          | RXD-a  | RXD    | Transmit   |

| 16         | RXD-b  | _      | Transmit   |

| 24         | ETC-a  | ETC    | Receive    |

| 11         | ETC-b  | _      | Receive    |

| 15         | TXC-a  | TXC    | Transmit   |

| 12         | TXC-b  | _      | Transmit   |

| 17         | RXC-a  | RXC    | Transmit   |

| 9          | RXC-b  | _      | Transmit   |

| 21         | ERC-a  | ERC    | Receive    |

| 18         | ERC-b  |        | Receive    |

| 4          | RTS-a  | RTS    | Receive    |

| 19         | RTS-b  | _      | Receive    |

| 20         | DTR-a  | DTR    | Receive    |

| 23         | DTR-b  | _      | Receive    |

| 6          | DSR-a  | DSR    | Transmit   |

| 22         | DSR-b  | _      | Transmit   |

| 5          | CTS-a  | CTS    | Transmit   |

| 13         | CTS-b  | _      | Transmit   |

| 8          | CD-a   | CD     | Transmit   |

| 10         | CD-b   | _      | Transmit   |

| 1,7        | GND    | GND    | _          |

In desktop design models, the digital port with a V.35 interface is equipped with a M-34 connector (female):

| Signal | Direction                                                                             |

|--------|---------------------------------------------------------------------------------------|

| TD-a   | Receive                                                                               |

| TD-b   | Receive                                                                               |

| RD-a   | Transmit                                                                              |

| RD-b   | Transmit                                                                              |

| ET-a   | Receive                                                                               |

| ET-b   | Receive                                                                               |

| TC-a   | Transmit                                                                              |

| TC-b   | Transmit                                                                              |

| ERC-a  | Receive                                                                               |

| ERC-b  | Receive                                                                               |

| RC-a   | Transmit                                                                              |

| RC-b   | Transmit                                                                              |

| RTS    | Receive                                                                               |

| DTR    | Receive                                                                               |

| DSR    | Transmit                                                                              |

| CTS    | Transmit                                                                              |

| DCD    | Transmit                                                                              |

| GND    | _                                                                                     |

| GND    | _                                                                                     |

|        | TD-a TD-b RD-a RD-b ET-a ET-b TC-a TC-b ERC-a ERC-b RC-a RC-b RTS DTR DSR CTS DCD GND |

Rear panel of the desktop design device (E1-DXC/B/3E1-V35-AC)

In desktop design models, the digital port with a universal interface is equipped with a HDB44 connector (female):

| Cont.         | V.35   | RS-530 | RS-232 | X.21          |

|---------------|--------|--------|--------|---------------|

| 10            | TXD-a  | TXD-a  | TXD    | Transmit(A)   |

| 25            | TXD-b  | TXD-b  |        | Transmit(B)   |

| 8             | RXD-a  | RXD-a  | RXD    | Receive(A)    |

| 9             | RXD-b  | RXD-b  | _      | Receive(B)    |

| 6             | ETC-a  | ETC-a  | ETC    | ETC(A)        |

| 7             | ETC-b  | ETC-b  |        | ETC(B)        |

| 2             | TXC-a  | TXC-a  | TXC    | SigTiming(A)  |

| <u>2</u><br>3 | TXC-b  | TXC-b  | _      | SigTiming(B)  |

| 5             | RXC-a  | RXC-a  | RXC    | _             |

| 4             | RXC-b  | RXC-b  | _      | _             |

| 17            | ERC-a  | ERC-a  | ERC    |               |

| 18            | ERC-b  | ERC-b  | _      | _             |

| 14            | RTS    | RTS-a  | RTS    | Control(A)    |

| 29            | _      | RTS-b  | _      | Control(B)    |

| <u>11</u>     | DTR    | DTR-a  | DTR    |               |

| 26            | _      | DTR-b  | _      |               |

| 13            | DSR    | DSR-a  | DSR    |               |

| 28            | _      | DSR-b  | _      |               |

| 15            | CTS    | CTS-a  | CTS    |               |

| 30            | _      | CTS-b  | _      |               |

| 12            | CD     | CD-a   | CD     | Indication(A) |

| 27            | _      | CD-b   | _      | Indication(B) |

| 1,16          | GND    | GND    | GND    | GND           |

| 31            | SEL-0* | SEL-0* | SEL-0* | SEL-0         |

| 33            | SEL-1  | SEL-1* | SEL-1  | SEL-1*        |

| 35            | SEL-2  | SEL-2  | SEL-2* | SEL-2         |

| 37            | SEL-3  | SEL-3* | SEL-3* | SEL-3*        |

| 39            | SEL-4* | SEL-4  | SEL-4  | SEL-4         |

| 41            | SEL-5* | SEL-5  | SEL-5  | SEL-5         |

| 43            | SEL-6* | SEL-6  | SEL-6  | SEL-6         |

| 32            | DCE    | DCE    | DCE    | DCE           |

\* - Connect the contact to GND

The Ethernet port is equipped with a RJ-45 connector (female):

| 1 | TD+      |

|---|----------|

| 2 | TD-      |

| 3 | RD+      |

| 4 | Not used |

| 5 | Not used |

| 6 | RD-      |

| 7 | Not used |

| 8 | Not used |

In 19" rack mounting design models the digital port with a universal interface is equipped with a MDB36 connector (female):

|       |        | ,      |        |               |

|-------|--------|--------|--------|---------------|

| Cont. | V.35   | RS-530 | RS-232 | X.21          |

| 17    | TXD-a  | TXD-a  | TXD    | Transmit(A)   |

| 18    | TXD-b  | TXD-b  | _      | Transmit(B)   |

| 12    | RXD-a  | RXD-a  | RXD    | Receive(A)    |

| 11    | RXD-b  | RXD-b  | _      | Receive(B)    |

| 19    | ETC-a  | ETC-a  | ETC    | ETC(A)        |

| 21    | ETC-b  | ETC-b  | _      | ETC(B)        |

| 32    | ERC-a  | ERC-a  | ERC    | SigTiming(A)  |

| 34    | ERC-b  | ERC-b  | _      | SigTiming(B)  |

| 3     | TXC-a  | TXC-a  | TXC    | _             |

| 4     | TXC-b  | TXC-b  | _      |               |

| 13    | RXC-a  | RXC-a  | RXC    | _             |

| 14    | RXC-b  | RXC-b  | _      |               |

| 15    | RTS    | RTS-a  | RTS    | Control(A)    |

| 16    | _      | RTS-b  | _      | Control(B)    |

| 1     | DTR    | DTR-a  | DTR    | _             |

| 2     | _      | DTR-b  | _      |               |

| 10    | DSR    | DSR-a  | DSR    | _             |

| 9     | _      | DSR-b  | _      | _             |

| 8     | CTS    | CTS-a  | CTS    | _             |

| 7     | _      | CTS-b  | _      |               |

| 6     | CD     | CD-a   | CD     | Indication(A) |

| 5     | _      | CD-b   | _      | Indication(B) |

| 20,22 | ,      | GND    | GND    | GND           |

| 24,26 | ,      |        |        |               |

| 28,30 |        |        |        |               |

| 23    | SEL-0* | SEL-0* | SEL-0* | SEL-0         |

| 25    | SEL-1  | SEL-1* | SEL-1  | SEL-1*        |

| 27    | SEL-2  | SEL-2  | SEL-2* | SEL-2         |

| 29    | SEL-3  | SEL-3* | SEL-3* | SEL-3*        |

| 31    | SEL-4* | SEL-4  | SEL-4  | SEL-4         |

| 33    | SEL-5* | SEL-5  | SEL-5  | SEL-5         |

| 35    | SEL-6* | SEL-6  | SEL-6  | SEL-6         |

| 36    | DCE    | DCE    | DCE    | DCE           |

|       |        |        |        |               |

<sup>\* -</sup> Connect the contact to GND

# Control via the console

The front panel of the multiplexing cross-connector is equipped with a DB9 (female) connector for connecting a control terminal (console) with RS-232 interface. The console may be used for viewing current device modes, link states, error statistics, for selecting device modes, and for storing them in nonvolatile RAM.

The console interface is designed as a simple hierarchical menu. To select a command, you must enter its number.

```

Cronyx E1-DXC /ETH revision B, 27/01/2004

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Statistics

2. Event counters

3. Loopback...

4. Test...

5. Configure...

0. Reset

Command:

```

The "Statistics" mode is used for viewing current information, link operating modes and statistic counters.

```

Statistics: Session #4, 0 days, 0:05:19

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

BPV

OOS

Status

Err

Event.

Link 0:

0

\cap

\cap

\cap

Ok

0

0

0

Link 1:

0

Ok

Link 2:

0

0

0

0

Ok

Port:

Ok

C - clear counters, R - refresh mode, any key to break...

```

The "C" key allows clearing error counters of a local device. The "R" key allows changing the display update mode.

| Counter | Error type                                                                    |

|---------|-------------------------------------------------------------------------------|

| BPV     | Line encoding violation                                                       |

| oos     | Number of seconds during which frame or multi-frame synchronization was lost  |

| Err     | For E1 links - number of seconds during which BER tester errors were present; |

|         | for serial ports - number of seconds during which external clock errors were  |

|         | present; for Ethernet ports - Ethernet bridge internal buffers overflow.      |

| Event   | Number of seconds, during which link-related events have taken place. The     |

|         | meaning of an event depends on the interface type.                            |

### Event counter values:

| Interface type     | Event             | Cause                                               |

|--------------------|-------------------|-----------------------------------------------------|

| Serial             | FIFO buffer error | 1. In the DTE2 mode (use of                         |

|                    |                   | ERC pulses) the requirement of-                     |

|                    |                   | common clock for the link                           |

|                    |                   | is not fulfilled.                                   |

|                    |                   | <ol><li>In mode with HDLC buffer disabled</li></ol> |

|                    |                   | too great clock frequency deviation                 |

|                    |                   | is present, which may mot be compensated            |

|                    |                   | by flag insertion/                                  |

|                    |                   | deletion.                                           |

| Async              | FIFO buffer error | Transmission rate or asynchronous                   |

|                    |                   | symbol format set for the-                          |

|                    |                   | port, do not correspond to connected-               |

|                    |                   | device settings.                                    |

|                    |                   | 2. Too large transmission rate                      |

|                    |                   | deviation in the connected device                   |

|                    |                   | from the rated value                                |

| IDSL               | FIFO buffer error | The requirement for common clock                    |

|                    |                   | in the link is not fulfilled                        |

| E1                 | Controlled slip   | The requirement for common clock                    |

|                    | (Slip-operation)  | in the link is not fulfilled                        |

| Ethernet Collision |                   | High Ethernet network segment                       |

|                    |                   | load                                                |

# The state of E1 links is shown as a set of flags:

| Flag   | Link state                                              |

|--------|---------------------------------------------------------|

| OK     | Normal mode, frame and multi-frame synchronism present  |

| LOS    | Loss of signal in the line                              |

| AIS    | Reception of alarm indication signal ("blue code")      |

| LOF    | Loss of frame synchronism                               |

| LOMF   | Loss of multi-frame synchronism                         |

| FARLOF | Loss of frame synchronism at the remote device          |

| AIS16  | Reception of alarm indication signal in timeslot 16     |

| RDMA   | Loss of CAS multi-frame synchronism at the remote modem |

| CRCE   | CRC error                                               |

| RCRCE  | CRC error at the remote modem                           |

#### The "Loopback" menu is designed for local loop control:

```

Loopback

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5, Loop

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Link 0 loop - enabled

2. Link 1 loop - disabled

3. Link 2 loop - disabled

Command:

```

#### The "Test" menu enables/disabled the built-in BER tester:

```

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5, Test

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Link 0 test - run

2. Link 1 test - stopped

3. Link 2 test - stopped

Command:

```

Loop and BER tester modes are not stored in the nonvolatile RAM.

The "Configure" menu allows selecting device operating modes:

```

Configure

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Sync & cross-connection...

2. Link 0...

3. Link 1...

4. Link 2...

5. Port...

7. Factory settings...

8. Save parameters

9. Restore parameters

Command:

```

After setting parameters, they must be saved in the multiplexer's nonvolatile RAM (NVRAM) using the "Save parameters" command. The last saved configuration parameters may be restored using the "Restore parameters" command.

The "Sync & cross-connection" menu allows to select master and backup clock, the timeslot 16 mode, and to go to the timeslot and Sa bits interchange map settings menu.

```

Sync & cross-connection

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Master clock: Int

3. Timeslot interchange map...

4. Timeslot 16: CAS

5. E1 link for port data: Link 0

6. Timeslots for port data...

7. Sa bits...

Command:

```

The "Timeslot interchange map" allows specifying the interrelationship between the output of single timeslot, and the input of another.

The "d" (data) symbol denotes timeslots used for data transmission. The fixed delay mode will be automatically specified for such timeslots. This mode maintains the integrity of the data stream transmitted over several timeslots.

The "v" (voice) symbol denotes timeslots occupied by voice telephone stream.

```

Timeslots interchange map

TS Link 0

Link 1

Link 2

Port

TS Link 0

Link 1

Link 2

Port

1 Port

d/L0/T1

17 Port

Idle

Idle

Idle

Idle

d/L0/T17

Idle

d/L0/T18

2 Port

Idle

Idle

d/L0/T2

18 Port

Idle

3 Port

Idle

Idle

d/L0/T3

19 Port

Idle

Idle

d/L0/T19

4 Port.

Idle

Idle

d/L0/T4

20 Port

Idle

Idle

d/L0/T20

Idle

Idle

Idle

Idle

5 Port

d/L0/T5

21 Port

d/L0/T21

6 Port

Idle

Idle

d/L0/T6

22 Port

Idle

Idle

d/L0/T22

7 Port

Idle

Idle

d/L0/T7

23 Port

Idle

Idle

d/L0/T23

Idle

d/L0/T8

Idle

d/L0/T24

8 Port

Idle

24 Port

Idle

Idle

Idle

25 Port

Idle

Idle

d/L0/T25

9 Port.

d/L0/T9

10 Port

Idle

Idle

d/L0/T10

26 Port

Idle

Idle

d/L0/T26

11 Port

Idle

Idle

d/L0/T11

27 Port

Idle

Idle

d/L0/T27

12 Port

Idle

Idle

d/L0/T12

Idle

Idle

d/L0/T28

28 Port

13 Port

Idle

Idle

d/L0/T13

29 Port

Idle

Idle

d/L0/T29

14 Port

Idle

Idle

d/L0/T14

30 Port

Idle

Idle

d/L0/T30

15 Port

Idle

d/L0/T15

Idle

Idle

d/L0/T31

Idle

31 Port

Link 0, Timeslot 1 : Data,

Transmit from Port

Arrow keys to move, <Enter> to edit, <Ctrl-C> to quit

```

In the 19" rack design, timeslots are always interchanges with a fixed delay, and specifying the "voice" - "data" mode is not required.

The "Sa bits interchange map" menu is used to specify the Sa bits interchange map:

```

Sa bits interchange map

Bit

Link 0

Link 1

Link 2

Link 1 Sa7 Set to "1"

Set to "1"

Set to "1"

Sa4

Set to "1"

Set to "1"

Sa5

Sa6

Set to "1"

Set to "1"

Set to "1"

Set to "1"

Set to "1"

Sa7

Link 0 Sa4

Sa8

Set to "1"

Set to "1"

Set to "1"

Link 0, Sa4: Transmit from Link 1, Sa7

Link 0 Sa bits:

0. Transmit from Link 0

1. Transmit from Link 1

2. Transmit from Link 2

4. Transmit all "1"

Arrow keys to move, <Enter> to edit, <Ctrl-C> to quit

```

The "Link 0" menu allows setting parameters for the E1/0 link:

```

Link 0

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

4. Crc4: No

5. Receiver gain: High

6. Idle code: 0xd5

7. Loss of sync action: Remote Alarm

Command:

```

To set parameter for other E1 links use menus "Link 1", "Link 2", and "Link 3" which are the same.

In models equipped with a digital port, the "Port" menu is used to set its parameters.

```

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

6. Duplex: Half

7. Filtering: Enabled

Command:

```

In order to speed up parameters setting it is possible to use one of the three factory presets for the most widespread types of multiplexer usage, with subsequent correction of some parameters:

```

Factory settings

Clocks: Active=Int, Master=Int, Timeslot16=CAS

Link 0: TP, High gain, no CRC4, Idle=0xd5

Link 1: TP, High gain, no CRC4, Idle=0xd5

Link 2: TP, High gain, no CRC4, Idle=0xd5

Port: 1920 kbps, 10Base-T Half Duplex

1. Empty

2. Loopback

3. Link 0 <-> Link 1, Link 2 <-> Port

Command:

```

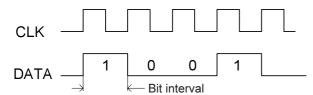

# Synchronous data transfer.

During synchronous data transfer, their modification is performed in strictly determined points of time, which are related to a special clock. The time during which data may not be modified, is called a bit interval. The receiver device must read data during points of time, which are close to the middle of the bit interval. Reading data at a bit interval boundary leads to faults. As a rule, the transmitter device modifies data at one of the clock signal edges, (for example, at the rising edge), and the receiver device reads the data at the other edge (the falling edge in this case).

Different interfaces use different clock signal transmission modes. V.35, RS-530, RS-232 etc., interfaces have special dedicated clock lines for each data direction (receive and transmit). Received RXD data are accompanied by RXC clock, and transmitted TXD data are accompanied by TXC clock.

Line modem interfaces (G.703, xDSL, etc.) use self-synchronizing codes (HDB3, Manchester, 2B1Q, etc.) to transmit data and clock over the same wires. The self-synchronizing codes are characterized by the fact that they do not contain long sequences of the same layer. This allows using the phase lock circuit at the receiver side to extract clock and data from the received signal.

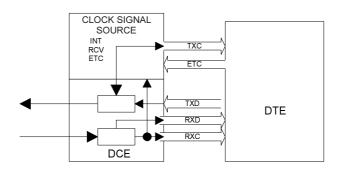

V.35, RS-530, RS-232 interfaces may be of DCE and DTE types. Modems have DCE interfaces, while computer-like devices have DTE. DCE device types are clock sources for both data transmission directions – both signals, the RXC (received data clock) and the TXC (transmitted data clock) are output signals for them. Here the RXC – is a signal received by the modem from the line, and extracted by the phase lock circuit. It accompanies the RXD data received by the modem and has the same direction.

Data received by the modem (TXD), are accompanied by the TXC clock. A DTE device serves as a TXD data signal source. The TXC clock comes from the modem, and its source may be an internal modem clock oscillator (INT), the clock signal extracted by the phase lock circuit from the signal received from the line (RCV), or an external clock source (EXT). As a rule, the external source is the signal received at the ETC interface input.

During serial data transfer, in addition to bit synchronization, there is need to determine byte boundaries. The stream is divided into frames for this purpose. The beginning of the frame serves as the byte reference point. In order to transmit digitized telephone data, the frame format described in the ITU G.704 recommendation is used. The HDLC standard is the most widely spread way to convert bit streams into frames in computer networks.

HDLC frame format

A certain bit sequence, called a flag, serves as a frame separator. In the HDLC protocol the flag is 01111110. In this case, in order for this sequence not to appear inside data, the staffing/destaffing procedure is used to insert/remove zeroes in a sequence of ones, which length exceeds five.

### Synchronous link design problems.

As a rule, synchronous links are designed on the common clock principle. This means that a data transmission link between two DTE devices uses a single clock to synchronize all data streams in the link. Clock is transmitted on the DCE-DTE device junction over special lines, and with the

help of self-synchronizing codes over communication lines. In a simplest case, when connecting two routers equipped with V.35 interfaces using synchronous modems for a dedicated line, the clock source is the internal oscillator of one of the modems (INT). The second modem extracts the clock from the signal received from the line (RCV). Both routers, as DTE devices, receive clock from modems.

Data are modified at the rising edge, and strobe at the falling edge.

An error situation is shown. Due to strobbing data input the DCE device during their modification

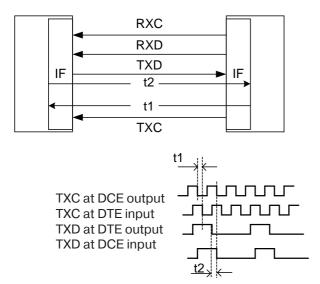

The problem that may arise even in this simplest case, is caused by the fact that the data received by the modem (TXD), and the clock accompanying them (TXC) have different directions, and are transmitted with delays. The TXC signal arrives to the DTE with a delay of t1, which is determined by internal modem circuits, connecting cables and the router interface. At the rising edge of the TXC signal, the router modifies the TXD data, which, after passing in the reverse direction, arrive to the modem with a delay of t2. If the sum of these two delays t1 + t2 is equal to the clock half-period, then data modification at the input comes precisely to the edge, which is used by the modem to sample data.

This leads to erroneous data reception from the router. The probability of such a situation increases as data transmission rate rises. This situation may be amended by inverting the TXC clock signal. This may be performed by changing the corresponding setting in the configuration of one of the devices.

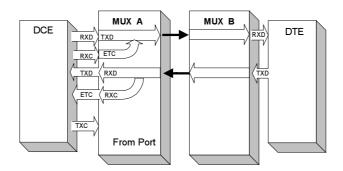

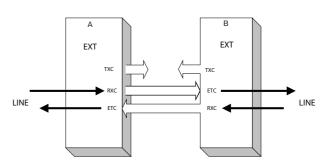

In some cases, there is a need to connect two DCE devices over V.35, RS-232, RS-530, etc. interface. The simplest way to make such a connection is to use the external clock mode for the transmitter path (EXT) for both devices.

Connection of two DCE devices over a digital interface.

The clock transmission path is shown.

In this mode, the modem transmits data to the line according to the clock signal received at the ETC interface input. The data received from the line by the first modem, and the accompanying clock signal arrives to RXD and RXC outputs. A special cable is used to supply them to, respectively, TXD and ETC inputs of the second modem, which transmits data and clock further to the line. The reverse stream passes over the same path. In this case the data and clock received from the line are relayed. This means that the clock source is external to the devices in question.

It is possible when the single device does not support the transmitter path synchronization from the external source (EXT). In this case, it is only possible to set the transmitter path synchronization from the ETC input for one of the modems. Here the modem that does not support this mode, will receive data at the TXD input using the clock from its internal clock source (INT) or received from the line (RCV).

Connection of two DCE devices over a digital interface.

Device B does not have a ETC input. The clock transmission path is shown.

If all devices used in the link, are configured to provide common clock, then the clock at the RXC output will have the same frequency (from the same source), as the clock in the transmitter path of the second modem. The link will operate without errors, if the phase shift between those two clocks is not equal to exactly half the period, the probability of which is quite low. In order to eliminate a situation completely, Cronyx synchronous modems support the DTE2 emulation mode. In this mode, the FIFO buffer is enabled on the digital interface in the received data path.

Connection of two DCE devices over a digital interface.

Device A uses a FIFO buffer. The clock transmission path is shown.

Data are put into the buffer according to the clock received from the line, and extracted according to the clock supplied to the ERC pins of the interface connector (external receiving clock). In this way, the FIFO buffer performs clock phase leveling. Here the Cronyx modem emulates a DTE interface, receiving transmission clock at the ETC input, and reception clock at the ERC input. The requirement for common clock is maintained. If there is no way to provide common clock in the link then the clock at one side of the buffer will have a different frequency compared to the clock at the other side of the buffer. This will lead to periodic buffer overflows or underflows, depending on which buffer side the clock has a higher frequency.

If data transmitted over a link are HDLC format packets, then this frequency discrepancy may be compensated using the fact that data in the HDLC stream have gaps filled with a special 01111110 bit sequence—the flag.

In Cronyx modems FIFO buffers may be switched to the HDLC mode. Here the control logic inserts HDLC flags between frames when the buffer tends to underflow, and removes excess HDLC flags when the buffer tends to overflow. The frequency discrepancy, which may be compensated in such a way, depends on HDLC packet length and the amount of flags between packets (this mode may not function when the number of flags between packets is less than two). For IP networks, the typical HDLC frame length is 1500 bytes, and the minimum number of flags between frames is 2. In this case the maximum frequency discrepancy, which may be compensated by such a buffer is at least 200 ppm.

# Cable wiring diagrams

# V.35 cable for model E1-DXC/B/3E1-M

| HDB44   | (male)                                                                                                           | M34 (female)                              |

|---------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 10      | ←                                                                                                                | Р                                         |

| 25      | •                                                                                                                | S                                         |

| 8       | <b></b>                                                                                                          | R                                         |

| 9       | <b>→</b>                                                                                                         | Т                                         |

| 6       | <b>←</b>                                                                                                         | U                                         |

| 7       | <b>←</b>                                                                                                         | W                                         |

| 2       | <b></b>                                                                                                          | Υ                                         |

| 3       | <b>→</b>                                                                                                         | AA                                        |

| 5       | <b>→</b>                                                                                                         | V                                         |

| 4       | <b>→</b>                                                                                                         | Χ                                         |

| 17      | <b>←</b>                                                                                                         | BB                                        |

| 18      | <b>←</b>                                                                                                         | Z                                         |

| 14      | <b>←</b>                                                                                                         | С                                         |

| 11      | <b>←</b>                                                                                                         | Н                                         |

| 13      | <b></b>                                                                                                          | E                                         |

| 15      | <b>→</b>                                                                                                         | D                                         |

| 12      | <b>→</b>                                                                                                         | F                                         |

| 1       | $\longleftrightarrow$                                                                                            | Α                                         |

| 16      | $\longleftrightarrow$                                                                                            | В                                         |

| 31,39,4 | 1,43                                                                                                             |                                           |

| connect | to GNE                                                                                                           | D 1                                       |

|         | 10<br>25<br>8<br>9<br>6<br>7<br>2<br>3<br>5<br>4<br>17<br>18<br>14<br>11<br>13<br>15<br>12<br>1<br>16<br>31,39,4 | 25 8 9 6 7 2 3 5 4 17 18 14 11 13 15 12 1 |

# RS-232 cable for model E1-DXC/B/3E1-M

| Signal | HDB4   | 4 (male)              | DB25 (female) |

|--------|--------|-----------------------|---------------|

| TXD    | 10     | <b>←</b>              | 2             |

| RXD    | 8      | <b>→</b>              | 3             |

| ETC    | 6      | <b>←</b>              | 24            |

| TXC    | 2      | <b>→</b>              | 15            |

| RXC    | 5      | <b></b>               | 17            |

| ERC    | 17     | ←                     | 21            |

| RTS    | 14     | ←                     | 4             |

| DTR    | 11     | <b>←</b>              | 20            |

| DSR    | 13     | <b>→</b>              | 6             |

| CTS    | 15     | <b></b>               | 5             |

| CD     | 12     | <b></b>               | 8             |

| GND    | 1      | $\longleftrightarrow$ | 1             |

| GND    | 16     | $\leftarrow$          | 7             |

| SEL-x  | 31,35, | 37                    |               |

|        | conne  | ct to GND 1           |               |

# RS-530 cable for model E1-DXC/B/3E1-M

| _      |         |            |               |

|--------|---------|------------|---------------|

| Signal | HDB44   | (male)     | DB25 (female) |

| TXD-a  | 10      | <b>←</b>   | 2             |

| TXD-b  | 25      | <b>←</b>   | 14            |

| RXD-a  | 8       | <b>→</b>   | 3             |

| RXD-b  | 9       | <b>→</b>   | 16            |

| ETC-a  | 6       | ←          | 24            |

| ETC-b  | 7       | ←          | 11            |

| TXC-a  | 2       | <b>→</b>   | 15            |

| TXC-b  | 3       | <b>→</b>   | 12            |

| RXC-a  | 5       | <b>→</b>   | 17            |

| RXC-b  | 4       | <b>→</b>   | 9             |

| ERC-a  | 17      | ←          | 21            |

| ERC-b  | 18      | ←          | 18            |

| RTS-a  | 14      | ←          | 4             |

| RTS-b  | 29      | <b>←</b>   | 19            |

| DTR-a  | 11      | ←          | 20            |

| DTR-b  | 26      | ←          | 23            |

| DSR-a  | 13      | <b>→</b>   | 6             |

| DSR-b  | 28      | <b>→</b>   | 22            |

| CTS-a  | 15      | <b>→</b>   | 5             |

| CTS-b  | 30      | <b>→</b>   | 13            |

| CD-a   | 12      | <b>→</b>   | 8             |

| CD-b   | 27      | <b>→</b>   | 10            |

| GND    | 1       | <b>←→</b>  | 1             |

| GND    | 16      | <b>←→</b>  | 7             |

| SEL-x  | 31,33,3 | 7          |               |

|        | connec  | t to GND 1 |               |

# X.21 cable for model E1-DXC/B/3E1-M

| HDB44   | (male)                                                                             | DB15 (female) |

|---------|------------------------------------------------------------------------------------|---------------|

| 10      | <b>←</b>                                                                           | 2             |

| 25      | ←                                                                                  | 9             |

| 8       | <b>→</b>                                                                           | 4             |

| 9       | <b>→</b>                                                                           | 11            |

| 6       | ←                                                                                  | 7             |

| 7       | <b>←</b>                                                                           | 14            |

| 2       | <b>→</b>                                                                           | 6             |

| 3       | <b>→</b>                                                                           | 13            |

| 14      | <b>←</b>                                                                           | 3             |

| 29      | <b>←</b>                                                                           | 10            |

| 12      | <b>→</b>                                                                           | 5             |

| 27      | <b>→</b>                                                                           | 12            |

| 1       | $\longleftrightarrow$                                                              | 1             |

| 16      | <b>←→</b>                                                                          | 8             |

| 33,37   | ·                                                                                  |               |

| connect | to GND 1                                                                           |               |

|         | 10<br>25<br>8<br>9<br>6<br>7<br>2<br>3<br>14<br>29<br>12<br>27<br>1<br>16<br>33,37 | 10            |

# RS-449 cable for model E1-DXC/B/3E1-M

| Signal | HDB44   | (male)                   | DB37 (fem    | ale) |

|--------|---------|--------------------------|--------------|------|

| TXD-a  | 10      | <b>←</b>                 | 4            |      |

| TXD-b  | 25      | <b>←</b>                 | 22           |      |

| RXD-a  | 8       | <b>→</b>                 | 6            |      |

| RXD-b  | 9       | <b>→</b>                 | 24           |      |

| ETC-a  | 6       | ←                        | 17           |      |

| ETC-b  | 7       | ←                        | 35           |      |

| TXC-a  | 2       | <b>→</b>                 | 5            |      |

| TXC-b  | 3       | <b>→</b>                 | 23           |      |

| RXC-a  | 5       | <b>→</b>                 | 8            |      |

| RXC-b  | 4       | <b>→</b>                 | 26           |      |

| ERC-a  | 17      | <b>←</b>                 | 3<br>21<br>7 |      |

| ERC-b  | 18      | ←                        | 21           |      |

| RTS-a  | 14      | ←                        | 7            |      |

| RTS-b  | 29      | ←                        | 25           |      |

| DTR-a  | 11      | ←                        | 12           |      |

| DTR-b  | 26      | ←                        | 30           |      |

| DSR-a  | 13      | <b>→</b>                 | 11           |      |

| DSR-b  | 28      | <b>→</b>                 | 29           |      |

| CTS-a  | 15      | <b>→</b>                 | 9            |      |

| CTS-b  | 30      | <b>→</b>                 | 27           |      |

| CD-a   | 12      | <b>→</b>                 | 13           |      |

| CD-b   | 27      | <b>→</b>                 | 31           |      |

| GND    | 1       | $\leftarrow \rightarrow$ | 1            |      |

| GND    | 16      | <b>←→</b>                | 19           |      |

| SEL-x  | 31,33,3 | 7                        |              |      |

|        |         | t to GND                 | 1            |      |

|        |         |                          |              |      |

# V.35 cable for connecting to DCE, for model E1-DXC/B/3E1-M

| Signal | HDB44 | 4 (male)                | M34 (1 | female) |

|--------|-------|-------------------------|--------|---------|

| TXD-a  | 10    | <b>←</b>                | R      | RXD-a   |

| TXD-b  | 25    | <b>←</b>                | Τ      | RXD-b   |

| RXD-a  | 8     | <b></b>                 | Р      | TXD-a   |

| RXD-b  | 9     | <b></b>                 | S      | TXD-b   |

| ETC-a  | 6     | ←                       | V      | RXC-a   |

| ETC-b  | 7     | <b>←</b>                | Χ      | RXC-b   |

| RXC-a  | 5     | <b>→</b>                | U      | ETC-a   |

| RXC-b  | 4     | <b></b>                 | W      | ETC-b   |

| RTS    | 14    | <b>←</b>                | F      | CD      |

| DTR    | 11    | <b>←</b>                | Е      | DSR     |

| DSR    | 13    | <b></b>                 | Н      | DTR     |

| CD     | 12    | <b></b>                 | С      | RTS     |

| TXC-a  | 2     | <b></b>                 | BB     | ERC-a   |

| TXC-b  | 3     | <b></b>                 | Z      | ERC-b   |

| ERC-a  | 17    | <b>←</b>                | Υ      | TXC-a   |

| ERC-b  | 18    | ←                       | AA     | TXC-b   |

| GND    | 1     | <b>←→</b>               | Α      | GND     |

| GND    | 16    | <b>←→</b>               | В      | GND     |

| SEL-x  |       | 41,43,32<br>ct to GND 1 |        |         |

|        |       |                         |        |         |

# V.35 cable for connecting to the Cronyx Tau-PCI board, for model E1-DXC/B/3E1-M

| Signal | HDB4             | 14                    | HDB26  | Signal   |

|--------|------------------|-----------------------|--------|----------|

|        | (male            | e) (male)             |        |          |

| TXD-a  | 10               | ←                     | 1      | TXD-a    |

| TXD-b  | 25               | ←                     | 2      | TXD-b    |

| RXD-a  | 8                | <b>→</b>              | 3      | RXD-a    |

| RXD-b  | 9                | <b>→</b>              | 24     | RXD-b    |

| ETC-a  | 6                | ←                     | 7      | TXCOUT-a |

| ETC-b  | 7                | ←                     | 9      | TXCOUT-b |

| RXC-a  | 5                | <b>→</b>              | 5      | RXCIN-a  |

| RXC-b  | 4                | <b>→</b>              | 15     | RXCIN-b  |

| RTS    | 14               | ←                     | 10     | RTS      |

| DTR    | 11               | ←                     | 19     | DTR      |

| DSR    | 13               | <b>→</b>              | 25     | DSR      |

| CD     | 12               | <b>→</b>              | 16     | CD       |

| TXC-a  | 2                | <b>→</b>              | 22     | TXCIN-a  |

| TXC-b  | 3                | <b>→</b>              | 23     | TXCIN-b  |

| ERC-a  | 17 Not connected |                       |        |          |

| ERC-b  | 18               | Not conr              | nected |          |

| GND    | 1                | $\longleftrightarrow$ | 11     | GND      |

| GND    | 16               | $\longleftrightarrow$ | 4,6,18 | GND      |

| SEL-x  | 31,39,41,43      |                       |        |          |